# HITACHI MOS LSI DATA BOOK LCD DRIVER LSI

# INDEX

|   |                                                                          | Page |

|---|--------------------------------------------------------------------------|------|

|   | GENERAL INFORMATION                                                      |      |

| • | QUICK REFERENCE GUIDE                                                    | 1    |

| • | PACKAGING INFORMATION                                                    | 3    |

| • | RELIABILITY AND QUALITY ASSURANCE                                        | 5    |

| • | RELIABILITY TEST DATA OF LCD DRIVERS                                     | 17   |

| • | FLAT PLASTIC PACKAGE (FPP) MOUNTING METHODS                              | 23   |

|   | LIQUID CRYSTAL DRIVING METHODS                                           | 27   |

|   | DATA SHEET                                                               |      |

| • | GENERAL PURPOSE LCD DRIVER                                               |      |

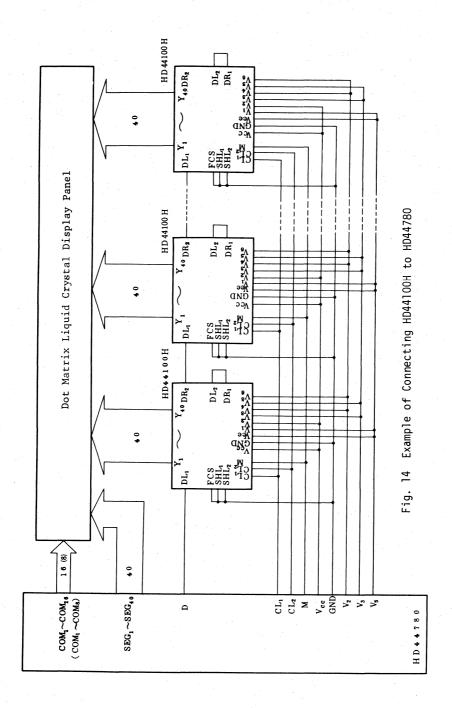

|   | HD44100H (LCD DRIVER WITH 40-CHANNEL OUTPUT)                             | 41   |

| • | CHARACTER DISPLAY TYPE                                                   |      |

|   | HD43160AH (CONTROLLER WITH BUILT-IN CHARACTER GENERATOR)                 | 49   |

|   | HD44780 (LCD-II) (DOT MATRIX LIQUID CRYSTAL DISPLAY CONTROLLER & DRIVER) | 65   |

|   | HD44101H (DOT MATRIX LIQUID CRYSTAL DISPLAY CONTROLLER & DRIVER)         | 115  |

| • | GRAPHIC DISPLAY TYPE                                                     |      |

|   | HD44102CH (DOT MATRIX LIQUID CRYSTAL GRAPHIC DISPLAY COLUMN DRIVER)      | 151  |

|   | HD44103CH (DOT MATRIX LIQUID CRYSTAL GRAPHIC DISPLAY COMMON DRIVER)      | 173  |

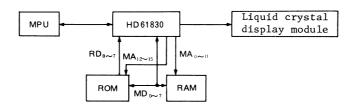

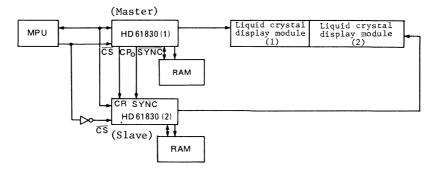

|   | HD61830 (DOT MATRIX LIQUID CRYSTAL GRAPHIC DISPLAY CONTROLLER)           | 183  |

| • | SEGMENT DISPLAY TYPE                                                     |      |

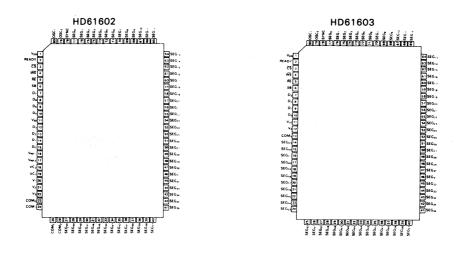

|   | HD61602/HD61603 (SEGMENT TYPE LCD DRIVER)                                | 209  |

# NOTICE

The example of an applied circuit or combination with other equipment shown herein indicates characteristics and performance of a semiconductor-applied products. The Company shall assume no responsibility for any problem involving a patent caused when applying the descriptions in the example.

# GENERAL INFORMATION

# QUICK REFERENCE GUIDE

# ■ LCD DRIVER SERIES CHARACTERISTICS

\*1: Except Power Supply for LCD.

\*2: -40-+85°C (Special Request). Please contact Hitachi Agents.

\*3: CG; Character Generator.

HITACH

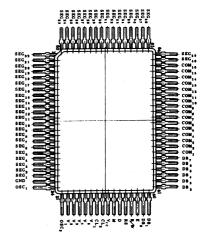

# PACKAGING INFORMATION

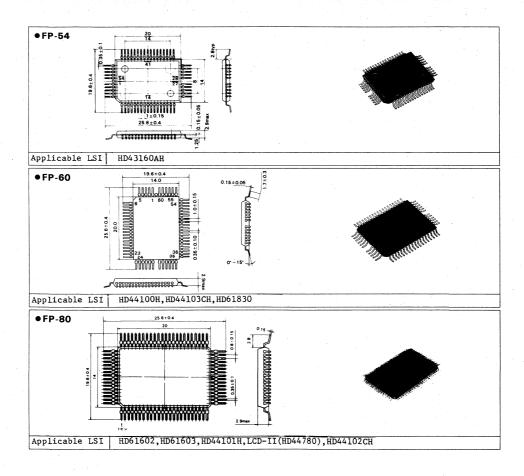

# ■ PACKAGE INFORMATION

The Hitachi LCD driver devices use plastic flat packages to make more compact the equipment in which they are incorporated and provide higher density mounting by utilizing the features of their thin liquid crystal display elements.

# ■ PACKAGE INFORMATION (UNIT: mm)

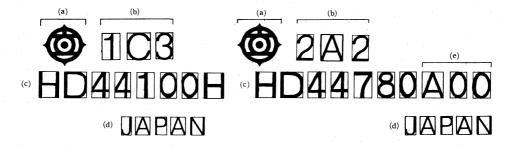

# **■** MARKING

There are two kinds of marking of the Hitachi LCD driver devices: the one with a standard type No. and the other with a ROM code. The type No. 2 with a ROM code is applied to the HD61830 and LCD II (HD44780).

(1) Standard type No.

(a) Type No. with ROM code

Meaning of each mark

| (a) | Hitachi mark      |

|-----|-------------------|

| (b) | Lot code          |

| (c) | Standard type No. |

| (d) | JAPAN mark        |

| (e) | ROM code          |

# RELIABILITY AND QUALITY ASSURANCE

#### VIEWS ON QUALITY AND RELIABILITY

Basic views on quality in Hitachi are to meet individual user's purchase purpose and quality required, and to be at the satisfied quality level considering general marketability. Quality required by users is specifically clear if the contract specification is provided. If not, quality required is not always definite. In both cases, efforts are made to assure the reliability so that semiconductor devices delivered can perform their ability in actual operating circumstances. To realize such quality in manufacturing process, the key points should be to establish quality control system in the process and to enhance moral for quality.

In addition, quality required by users on semiconductor devices is going toward higher level as performance of electronic system in the market is going toward higher one and is expanding size and application fields. To cover the situation, actual bases Hitachi is performing is as follows;

- (1) Build the reliability in design at the stage of new product development.

- (2) Build the quality at the sources of manufacturing process.

- (3) Execute the harder inspection and reliability confirmation of final products.

- (4) Make quality level higher with field data feed back.

- (5) Cooperate with research laboratories for higher quality and reliability.

With the views and methods mentioned above, utmost efforts are made for users' requirements.

#### 2. RELIABILITY DESIGN OF SEMICONDUCTOR DEVICES

#### 2.1 Reliability Targets

Reliability target is the important factor in manufacture and sales as well as performance and price. It is not practical to rate reliability target with failure rate at the certain common test condition. The reliability target is determined corresponding to character of equipments taking design, manufacture, inner process quality control, screening and test method, etc. into consideration, and considering operating circumstances of equipments the semiconductor device used in, reliability target of system, derating applied in design, operating condition, maintenance, etc.

#### 2.2 Reliability Design

To achieve the reliability required based on reliability targets, timely study and execution of design standardization, device design (including process design, structure design), design review, reliability test are essential.

#### (1) Design Standardization

Establishment of design rule, and standardization of parts, material and process are necessary. As for design rule, critical items on quality and reliability are always studied at circuit design, device design, layout design, etc. Therefore, as long as standardized process, material, etc. are used, reliability risk is extremely small even in new development devices, only except for in the case special requirements in function needed.

# (2) Device Design

It is important for device design to consider total balance of process design, structure design, circuit and layout design. Especially in the case new process and new material are employed, technical study is deeply executed prior to device development.

#### (3) Reliability Evaluation by Test Site

Test site is sometimes called Test Pattern. It is useful method for design and process reliability evaluation of IC and LSI which have complicated functions.

#### 1. Purposes of Test Site are as follows;

- · Making clear about fundamental failure mode

- Analysis of relation between failure mode and manufacturing process condition

- · Search for failure mechanism analysis

- · Establishment of QC point in manufacturing

#### 2. Effectiveness of evaluation by Test Site are as follows;

Common fundamental failure mode and failure mechanism in devices can be evaluated.

- Factors dominating failure mode can be picked up, and comparison can be made with process having been experienced in field.

- Able to analyze relation between failure causes and manufacturing factors.

- Easy to run tests.

etc.

#### 2.3 Design Review

Design review is organized method to confirm that design satisfies the performance required including users' and design work follows the specified ways, and whether or not technical improved items accumulated in test data of individual major fields and field data are effectively built in. In addition, from the standpoint of enhancement of competitive power of products, the major purpose of design review is to ensure quality and reliability of the products. In Hitachi, design review is performed from the planning stage for new products and even for design changed products. Items discussed and determined at design review are as follows;

- (1) Description of the products based on specified design documents.

- (2) From the standpoint of specialty of individual participants, design documents are studied, and if unclear matter is found, sub-program of calculation, experiments, investigation, etc. will be carried out.

- (3) Determine contents of reliability and methods, etc. based on design document and drawing.

- (4) Check process ability of manufacturing line to achieve design goal.

- (5) Discussion about preparation for production.

- (6) Planning and execution of sub-programs for design change proposed by individual specialist, and for tests, experiments and calculation to confirm the design change.

- (7) Reference of past failure experiences with similar devices, confirmation of method to prevent them, and planning and execution of test program for confirmation of them. These studies and decisions are made using check lists made individually depending on the objects.

# 3. QUALITY ASSURANCE SYSTEM OF SEMICONDUCTOR DEVICES

## 3.1 Activity of Quality Assurance

General views of overall quality assurance in Hitachi are as follows;

- Problems in individual process should be solved in the process. Therefore, at final product stage, the potential failure factors have been already removed.

- (2) Feedback of information should be made to ensure satisfied level of process ability.

- (3) To assure reliability required as an result of the things mentioned above is the purpose of quality assurance.

The followings are regarding device design, quality approval at mass production, inner process quality control, product inspection and reliability tests.

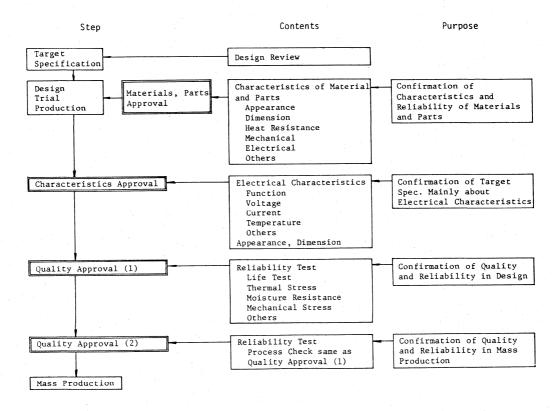

## 3.2 Quality Approval

To ensure quality and reliability required, quality approval is carried out at trial production stage of device design and mass production stage based on reliability design described at section 2.

The views on quality approval are as follows;

- The third party performs approval objectively from the standpoint of customers.

- (2) Fully consider past failure experiences and information from field.

- (3) Approval is needed for design change and work change.

- (4) Intensive approval is executed on parts material and process.

- (5) Study process ability and fluctuation factor, and set up control points at mass production stage.

Considering the views mentioned above, quality approval shown in Fig. 1 is performed.

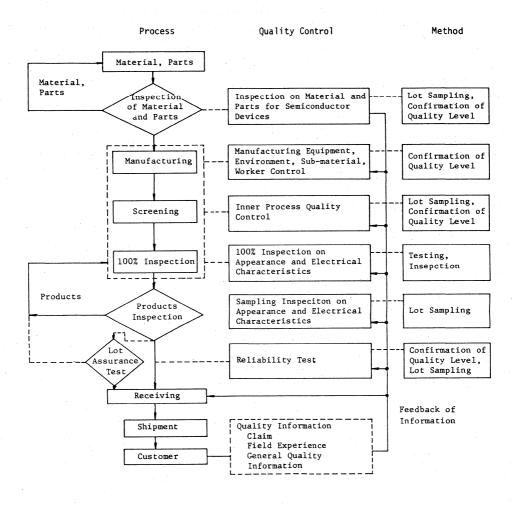

# 3.3 Quality and Reliability Control at Mass Production

For quality assurance of products in mass production, quality control is executed with organic division of functions in manufacturing department, quality assurance department, which are major, and other departments related. The total function flow is shown in Fig. 2. The main points are described below.

# 3.3.1 Quality Control of Parts and Material

As the performance and the reliability of semiconductor devices are getting higher, importance is increasing in quality control of material and parts, which are crystal, lead frame, fine wire for wire bonding, package, to build products, and materials needed in manufacturing process, which are mask pattern and chemicals. Besides quality approval on parts and materials stated in section 3.2, the incoming inspection is, also, key in quality control of parts and materials. The incoming inspection is performed based on incoming inspection specification following purchase specification and drawing, and sampling inspection is executed based on MIL-STD-105D mainly.

The other activities of quality assurance are as follows:

Fig. 1 Flow Chart of Quality Approval

- (1) Outside Vendor Technical Information Meeting

- (2) Approval on outside vendors, and guidance of outside vendors

- (3) Physical chemical analysis and test

The typical check points of parts and materials are shown in Table 1.

### 3.3.2 Inner Process Quality Control

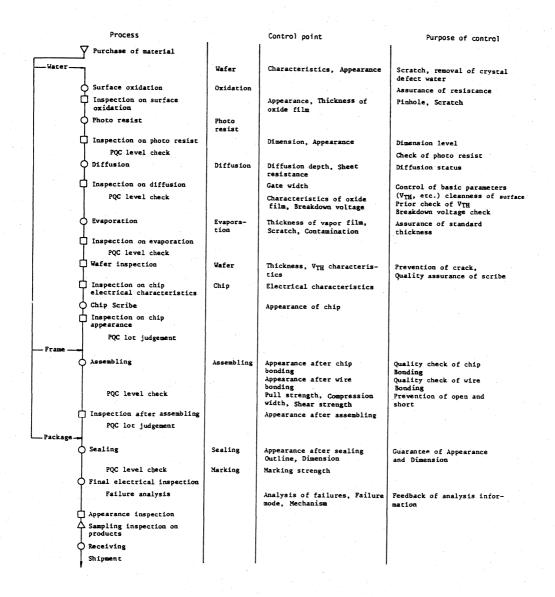

Inner process quality control is performing very important function in quality assurance of semiconductor devices. The following is description about control of semi-final products, final products, manufacturing facilities, measuring equipments, circumstances and sub-materials. The quality control in the manufacturing process is shown in Fig. 3 corresponding to the manufacturing process.

(1) Quality Control of Semi-final Products and Final Products

Potential failure factors of semiconductor devices should be removed preventively in manufacturing process. To achieve it, check points are set—up in each process, and products which have potential failure factor are not transfer to the next process. Especially, for high reliability semiconductor devices, manufacturing line is rigidly selected, and the quality control in the manufacturing process is tightly executed—rigid check in each process and each lot, 100% inspection in appropriate ways to remove failure factor caused by manufacturing fluctuation, and execution of screening needed, such as high temperature aging and temperature cycling. Contents of inner process quality control are as follows:

- Condition control on individual equipments and workers, and sampling check of semifinal products.

- · Proposal and carrying-out improvement of work

- · Education of workers

- · Maintenance and improvement of yield

- · Picking-up of quality problems, and execution of counter-measures

- · Transmission of information about quality

- (2) Quality Control of Manufacturing Facilities and Measuring Equipment

Equipments for manufacturing semiconductor devices have been developing extraordinarily with necessary high performance devices and improvement

of production, and are important factors to determine quality and reliability. In Hitachi, automatization of manufacturing equipments are promoted to improve manufacturing fluctuation, and controls are made to maintain proper operation of high performance equipments and perform the proper function. As for maintenance inspection for quality control, there are daily inspection which is performed daily based on specification related, and periodical inspection which is performed periodically. At the inspection, inspection points listed in the specification are checked one by one not to make any omission. As for adjustment and

Fig. 2 Flow Chart of Quality Control in Manufacturing Process

maintenance of measuring equipments, maintenance number, specification are checked one by one to maintain and improve quality.

(3) Quality Control of Manufacturing Circumstances and Submaterials

Quality and reliability of semiconductor device is highly affected by manufacturing process. Therefore, the controls of manufacturing circumstances - temperature, humidity, dust - and the control of submaterials - gas, pure water - used in manufacturing process are intensively executed. Dust control is described in more detail below.

Dust control is essential to realize higher integration and higher reliability of devices. In Hitachi, maintenance and improvement of cleanness in manufacturing site are executed with paying intensive attention on buildings, facilities, airconditioning systems, materials deliveredin, clothes, work, etc., and periodical inspection on floating dust in room, falling dusts and dirtiness of floor.

# 3.3.3 Final Product Inspection and Reliability Assurance

# (1) Final Product Inspection

Lot inspection is done by quality assurance department for products which were judged as good products in 100% test, which is final process in manufacturing department. Though 100% of good products is expected, sampling inspection is executed to prevent mixture of failed products by mistake of work, etc. The inspection is executed not only to confirm that the products meet users' requirement, but to consider potential factors. Lot inspection is executed based on MIL-STD-105D.

# (2) Reliability Assurance Tests

To assure reliability of semiconductor devices, periodical reliability tests and reliability tests on individual manufacturing lot required by user are performed.

Table l Quality Control Check Points of Material and Parts (Example)

| Material,<br>parts                  | Important<br>control items                                                                                           | Point for check                                                                                                     |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Water                               | Appearance  Dimension Sheet resistance Defect density Crystal axis                                                   | Damage and contamination<br>on surface<br>Flatness<br>Resistance<br>Defect numbers                                  |

| Mask                                | Appearance<br>Dimension<br>Resistoration<br>Gradation                                                                | Defect numbers, scratch<br>Dimension level<br>Uniformity of gradation                                               |

| Fine<br>wire for<br>wire<br>bonding | Appearance Dimension Purity Elongation ratio                                                                         | Contamination, scratch,<br>bend, twist<br>Purity level<br>Mechanical strength                                       |

| Frame                               | Appearance Dimension Processing accuracy Plating Mounting characteristics                                            | Contamination, scratch Dimension level  Bondability, solderability Heat resistance                                  |

| Ceramic<br>package                  | Appearance Dimension Leak resistance Plating Mounting characteristics Electrical characteristics Mechanical strength | Contamination, scratch Dimension level Airtightness Bondability, solderability Heat resistance  Mechanical strength |

| Plastic                             | Composition  Electrical characteristics Thermal characteristics Molding performance Mounting characteristics         | Characteristics of plastic material  Molding performance  Mounting characteristics                                  |

Fig. 3 Example of Inner Process Quality Control

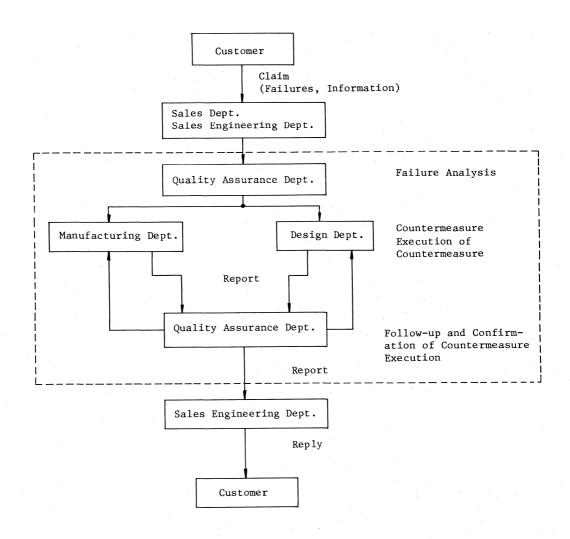

Fig. 4 Process Flow Chart of Field Failure

# RELIABILITY TEST DATA OF LCD DRIVERS

#### INTRODUCTION

The use of liquid crystal displays with microcomputer application systems has been increasing, because of their merits such as low power consumption, freedom in display pattern design, and thin shape. Low power consumption and high density packaging have been achieved through the use of the CMOS process and the flat plastic packages, respectively.

This chapter describes reliability and quality assurance data for Hitachi LCD driver LSIs based on test data and failure analysis results.

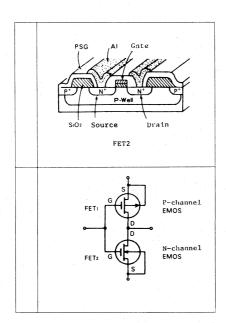

#### CHIP AND PACKAGE STRUCTURE

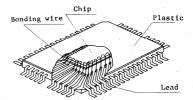

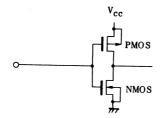

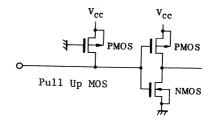

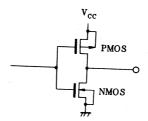

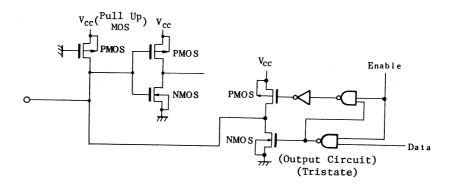

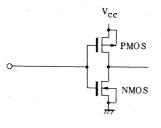

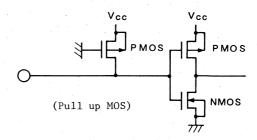

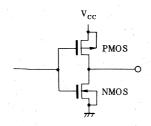

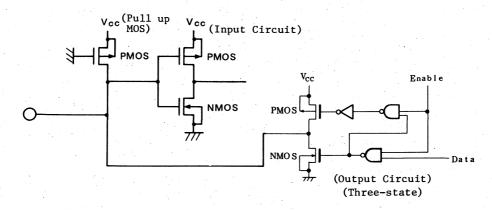

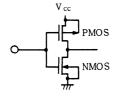

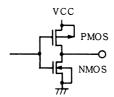

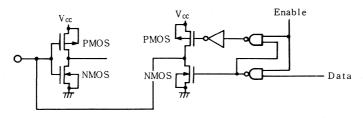

Hitachi LCD driver LSI family are produced in low power CMOS technology and flat plastic package. Si-gate process is used for high reliability and high density. Chip structure and basic circuit are shown in Fig. 1, and package structure is shown in Fig. 2.

Fig. 2 Package Structure

Fig. 1 Chip Structure and Basic Circuit

# 3. RELIABILITY TEST RESULTS

The test results of LCD Driver LSI family are shown in Table 1, 2 and 3.

Table 1 Test Result (1), High Temperature Operation  $(Ta=125^{\circ}C, V_{CC}=5.5V, V_{EE}=-5.5V)$

| Device    | Sample size | Component hour | Failure |

|-----------|-------------|----------------|---------|

| НD44100Н  | 40          | 40,000         | 0       |

| нD44101н  | 40          | 20,000         | 0       |

| HD44102CH | 40          | 40,000         | 0       |

| HD44103CH | 40          | 40,000         | 0       |

| HD44780   | 90          | 90,000         | 0       |

| Total     | 250         | 230,000        | 0       |

Table 2 Test Result (2)

| Test item                              | Test condition          | Sample<br>size | Component<br>hour | Failure |

|----------------------------------------|-------------------------|----------------|-------------------|---------|

| High temp, storage Ta=150°C, 1000 hrs. |                         | 90             | 900,000           | 0       |

| Low temp, storage                      | Ta=-55°C, 1000 hrs.     | - 80           | 800,000           | 0       |

| Steady state humidity                  | 65°C, 95% RH, 1000 hrs. | 545            | 550,000           | 1*1     |

| Steady state humidity biased           | 85°C, 90% RH, 1000 hrs. | 165            | 170,000           | 2*2     |

| Pressure cooker                        | 121°C, 2 ATM. 96 hrs.   | 55             | 5,300             | 0       |

\*1, \*2: Aluminum corrosion

Table 3 Test Results (3)

| Test items          | Test condition             | Sample size | Failure |

|---------------------|----------------------------|-------------|---------|

| Thermal shock       | 0 ~ 100°C<br>10 cycles     | 108         | 0       |

| Temperature cycling | -55°C ~ 150°C<br>10 cycles | 678         | 0       |

| Soldering heat      | 260°C 10 sec.              | 132         | 0       |

| Solderability       | 230°C 5 sec.               | 43          | 0       |

#### 4. QUALITY DATA FROM FIELD USE

Field failure rate is estimated in advance through production process evaluation and reliability tests. Past field data on similar devices provides the basis for this estimation. Quality information from the users are indispensable to the improvement of products quality. Therefore, field data on products delivered to the users are followed up carefully. On the basis of information furnished by the user, failure analysis is conducted and the results are quickly fed back to the design and production divisions.

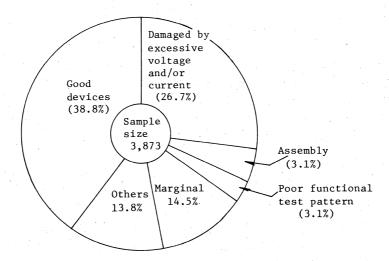

Failure analysis result on MOS LSI returned to Hitachi is shown in Fig. 3.

Fig. 3 Failure Analysis Result

#### 5. PRECAUTION

### 5.1 Storage

It is preferable to store semiconductor devices in the following ways to prevent detrioration in their electrical characteristics, solderability, and appearance, or breakage.

- (1) Store in an ambient temperature of 5 to 30°C, and in a relative humidity of 40 to 60%.

- (2) Store in a clean air environment, free from dust and active gas.

- (3) Store in a container which does not induce static electricity.

- (4) Store without any physical load.

- (5) If semiconductor devices are stored for a long time, store them in the unfabricated form. If their lead wires are formed beforehand, bent parts may corrode during storage.

- (6) If the chips are unsealed, store them in a cool, dry, dark, and dustless place. Assemble them within 5 days after unpacking. Storage in nitrogen gas is desirable. They can be stored for 20 days or less in dry nitrogen gas with a dew point at  $-30\,^{\circ}\text{C}$  or lower. Unpacked devices must not be stored for over 3 months.

- (7) Take care not to allow condensation during storage due to rapid temperature changes.

### 5.2 Transportation

As with storage methods, general precautions for other electronic component parts are applicable to the transportation of semiconductors, semiconductorincorporating units and other similar systems. In addition, the following considerations must be given, too:

- (1) Use containers or jigs which will not induce static electricity as the result of vibration during transportation. It is desirable to use an electrically conductive container or aluminium foil.

- (2) In order to prevent device breakage from clothes-induced static electricity, workers should be properly grounded with a resistor while handling devices. The resistor of about 1 M ohm must be provided near the worker to protect from electric shock.

- (3) When transporting the printed circuit boards on which semiconductor devices are mounted, suitable preventive measures against static electricity induction must be taken; for example, voltage built-up is prevented by shorting terminal circuit. When a belt conveyor is used, prevent the conveyor belt from being electrically charged by applying some surface treatment.

- (4) When transporting semiconductor devices or printed circuit boards. minimize mechanical vibration and shock.

### 5.3 Handling for Measurement

Avoid static electricity, noise and surge-voltage when semiconductor devices are measured. It is possible to prevent breakage by shorting their terminal circuits to equalize electrical potential during transportation. However, when the devices are to be measured or mounted, their terminals are left open to provide the possibility that they may be accidentally touched by a worker, measuring instrument, work bench, soldering iron, belt conveyor, etc. The device will fail if it touches something which leaks current or has a static charge. Take care not to allow curve tracers, synchroscopes, pulse generators, D.C. stabilizing power supply units etc. to leak current through their terminals or housings.

Especially, while the devices are being tested, take care not to apply surge voltage from the tester, to attach a clamping circuit to the tester, or not to apply any abnormal voltage through a bad contact from a current source.

During measurement, avoid miswiring and short-circuiting. When inspecting a printed circuit board, make sure that no soldering bridge of foreign matter exists before turning on the power switch.

Since these precautions depend upon the types of semiconductor devices, contact Hitachi for further details.

# FLAT PLASTIC PACKAGE (FPP) MOUNTING METHODS

The FPP can obtain better space factors than DIP type because the board occupying area and thickness can be reduced. No through holes nor lead forming is required for mounting the board. Therefore, the FPP can be mounted as it is, and is suitable for automatic mounting, providing remarkable reduction of manpower.

Various mounting methods are provided and can be used for each purpose. typical example of mounting are given below.

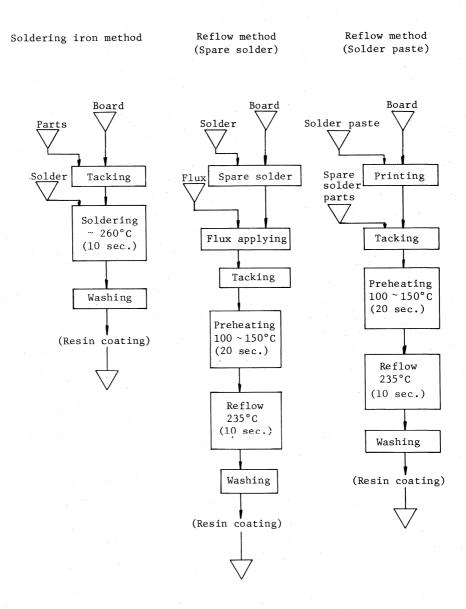

#### 1. Individual Mounting with Soldering Iron

A method used mainly in the trial and small-scale production of circuits. The FPP can be soldered by fixing it on the mounting part of the printed circuit board with flux or adhesive agent while pressing it. For mounting, sharpen the tip of soldering iron or make it in a block shape so that more than one pin can be heated simultaneously. Use a fine solder (about  $\phi$  0.5mm). Solder within 10 seconds per IC at the maximum temperature of 260°C for lead and 235°C for resin part (lead bottom) as the heating conditions.

#### 2. Reflow Soldering

The reflow soldering is the most general method in which the chips such as a transistor, a resistor and a capacitor are mounted on a hybrid IC. It can be also applied to the FPP. (Note) In addition, there are methods in which spare soldering and flux are applied to a printed circuit board in advance and in which solder paste is selectively applied to a printed circuit board by screen process printing.

The FPP is tacked at a specified position with flux or solder paste. However, a small amount of adhesive can be applied to the rear of FPP for temporary fixing. Spare solder is melted by passing the board whose parts are tacked, through a temperature-controlled hot plate or conveyor type heater. Then the board can be soldered. In this case, preheat thoroughly to eliminate the thermal distortion of board and mounted parts. Pay attention to temperature control in consideration of the heat absorption of black plastic caused by an infrared-ray heater. As the heating conditions, preheat the board and parts for 20 seconds at a temperature of 100 to 150°C. Then heat them within 10 seconds at the maximum temperature of

$235\,^{\circ}\text{C}$  as a resin surface temperature . If the board is directly heated from the upper side of FPP with an infrared-ray heater, the temperature of resin surface becomes higher than the lead. Therefore, a shielding plate or similar thing must be used so that the temperature of resin surface can be  $235\,^{\circ}\text{C}$  or below.

(Note) Reflow soldering can be applied to the 2.9 mm (Max.) thick FPP used in the LCD driver series. However, the FPPs of 2.4 mm (Max.) and 1.5 mm (Max.) in thickness cannot be used for reflow soldering under the above conditions.

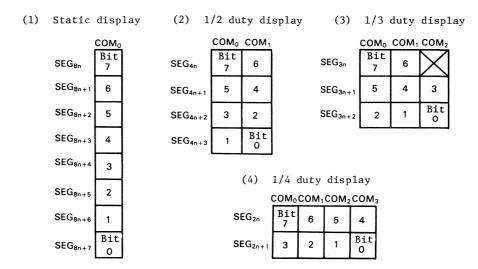

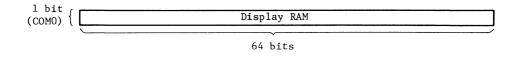

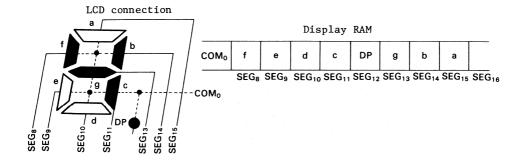

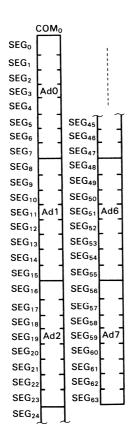

# LIQUID CRYSTAL DRIVING METHODS

Driving a liquid crystal at direct current triggers electrode reaction inside the liquid cell, deteriorating display quality rapidly. The liquid crystal must be driven at alternating current. The AC driving method includes the static driving method and the multiplex driving method, each of which has the features and can be used for applications. Hitachi has been developping the LCD driver devices corresponding to the static driving method and the multiplex driving method. The following sections describe the features of each driving method, the driving waveforms and how to apply bias.

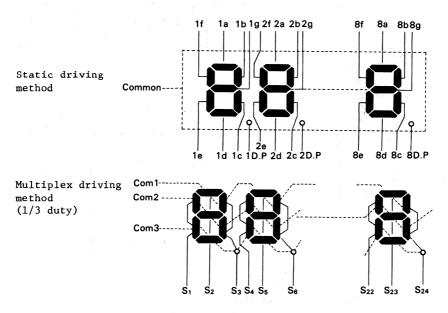

#### ■ STATIC DRIVING METHOD

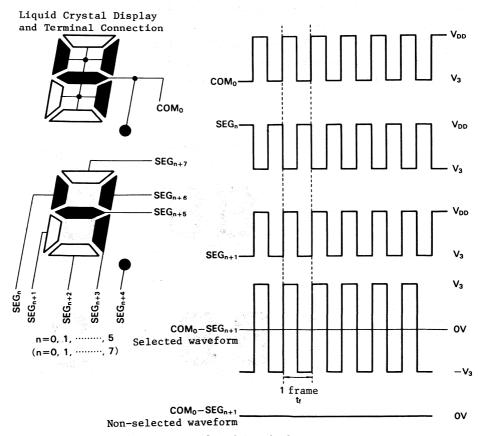

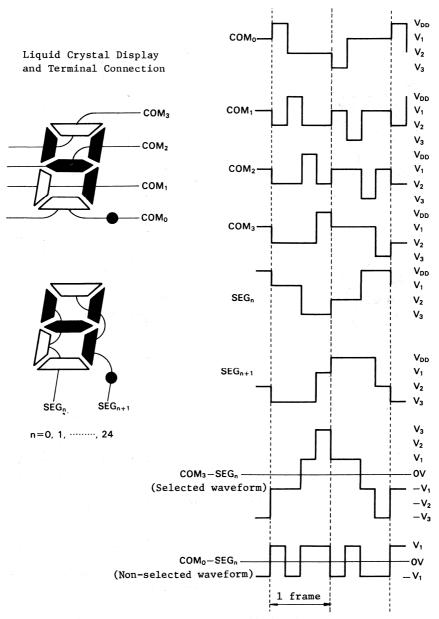

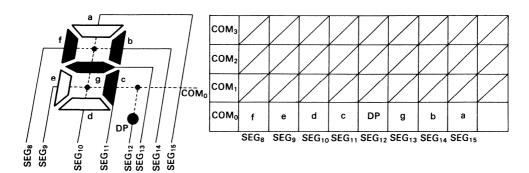

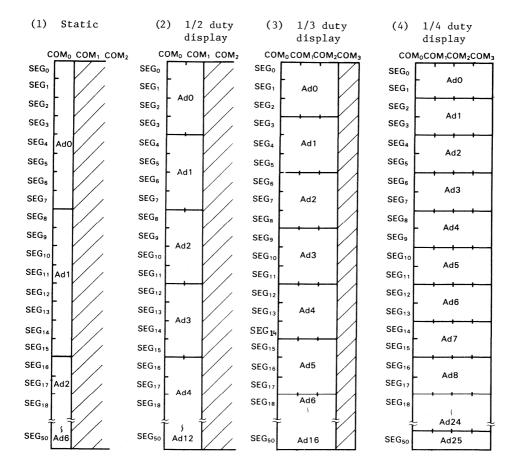

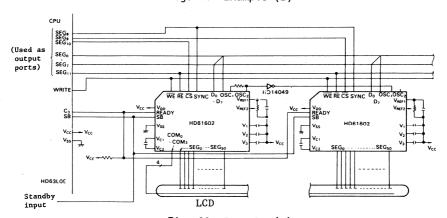

Fig. 1 Example of Static Drive Waveforms (Example of HD61602/HD61603)

Fig. 1 shows the driving waveforms of the static driving method and an example in which "4" is displayed in the segment method. The static driving method is the most basic method in which good display quality can be obtained. However, it is not suitable for the display of the liquid crystal with many segments because one liquid crystal driver circuit is required per segment. The static driving method is used at the frame frequency  $(1/t_f)$  of several tens to several hundreds Hz.

#### ■ MULTIPLEX DRIVING METHOD

The multiplex driving method is effective in reducing the number of driver circuits, the number of connections between the circuit and the display cell, and the cost when driving many display picture elements. Fig. 2 shows the comparision of the static drive with the multiplex drive (1/3 duty) in 8-digit numeric display. The number of liquid crystal driver circuits required is 65 for the former and 27 for the latter. The multiplex drive reduces the number of driver circuits. However, the more multiplexed, the

Fig. 2 Example of Comparision of Static Drive with Multiplex Drive

smaller the driving voltage tolerance. Thus, there are limits to extent of multiplexing.

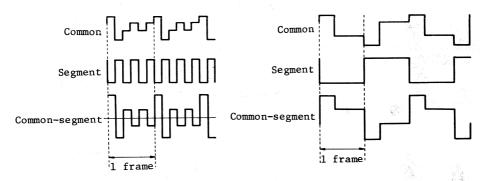

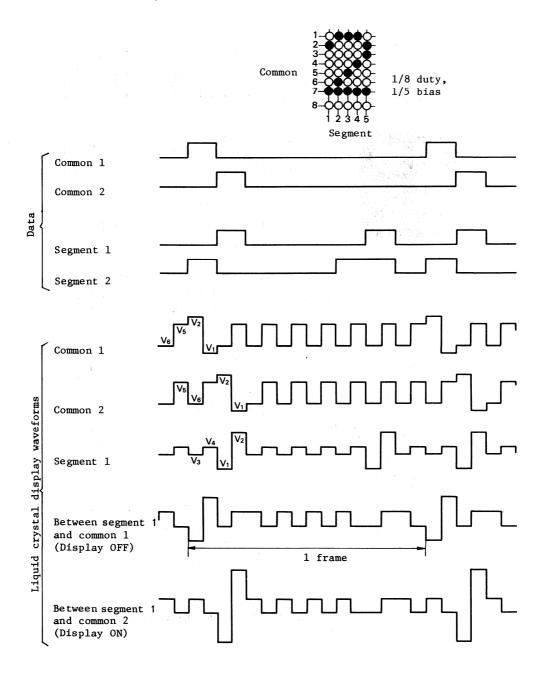

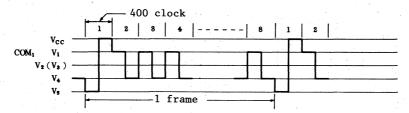

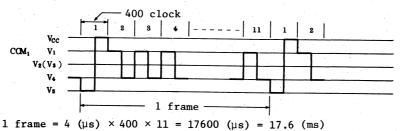

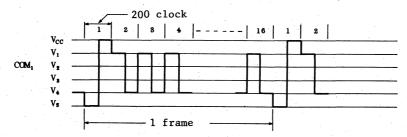

There are two types of multiplex drive waveforms: A type and B type. A type, shown in Fig. 3, is used for alternation in 1 frame. B type is used for alternation in between 2 frames. B type has better display quality than A type in high multiplex drive.

Fig. 3 A Type Waveforms (1/3 duty, 1/3 bias)

Fig. 4 B Type Waveforms (1/3 duty, 1/3 bias)

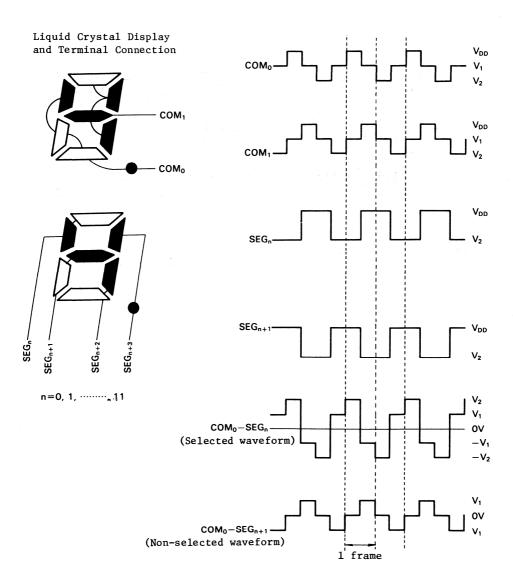

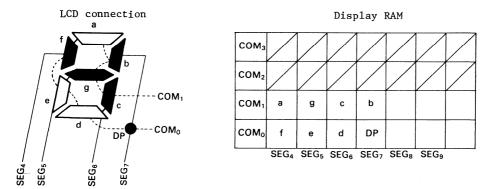

# ●1/2 Bias, 1/2 Duty Drive

In the 1/2 duty drive, 1 driver circuit drives 2 segments. Fig. 5 shows an example of the connection in displaying '4' on the liquid crystal display of 7-segment type, and the output waveforms.

Fig. 5 Example of Waveforms in 1/2 Duty Drive (B type) (Example of HD61602)

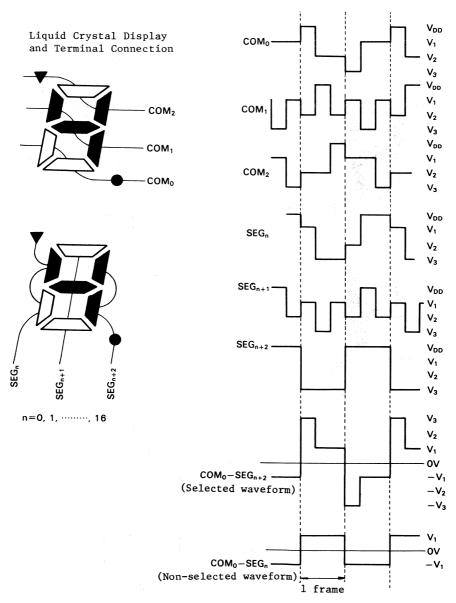

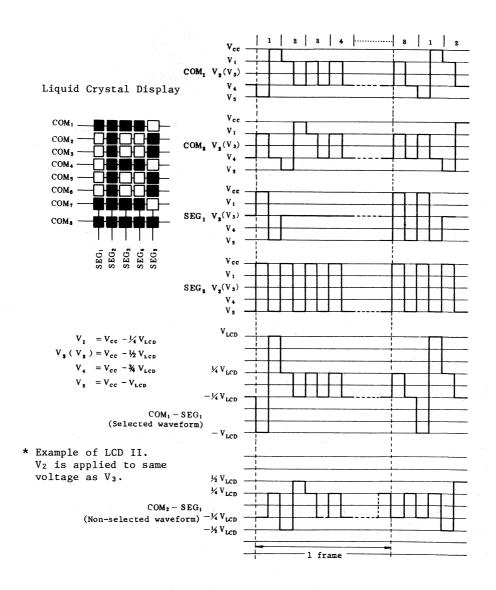

# ● 1/3 Bias, 1/3 Duty Drive

In the 1/3 duty drive, 3 segments are driven by 1 segment output driver. Fig. 6 shows an example of the connection in displaying '4' on the liquid crystal display of 7-segment type, and the output waveforms.

Fig. 6 Example of Waveforms in 1/3 Duty Drive (B type) (Example of HD61602)

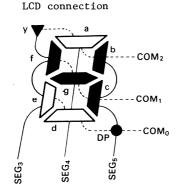

### ● 1/3 Bias, 1/4 Duty Drive

In the 1/4 duty drive, 4 segments are driven by 1 segment output driver. Fig. 7 shows an example of the connection in displaying '4' on the liquid crystal of 7-segment type, and the output waveforms.

Fig. 7 Example of Waveforms in 1/4 Duty Drive (B type) (Example of HD61602)

Fig. 8 Example of Waveforms in 1/8 Duty Drive (A type) (Example of LCD-II)

Fig. 9 Example of Waveforms in 1/8 Duty Drive (A type) (Example of HD44100H)

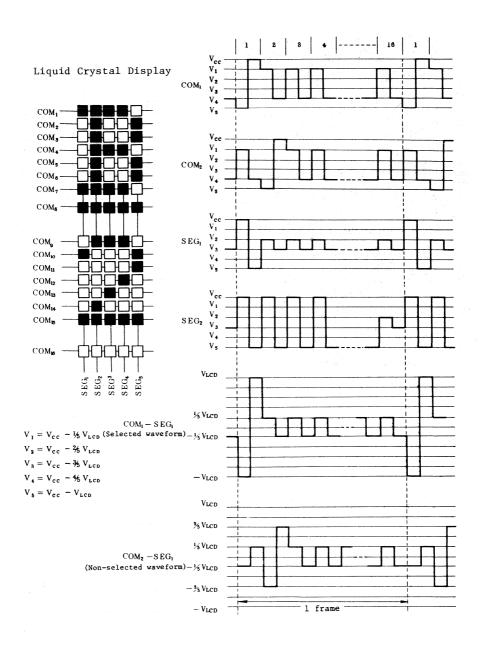

Fig. 10 Example of Waveforms in 1/16 Duty Drive (A type) (Example of LCD-II)

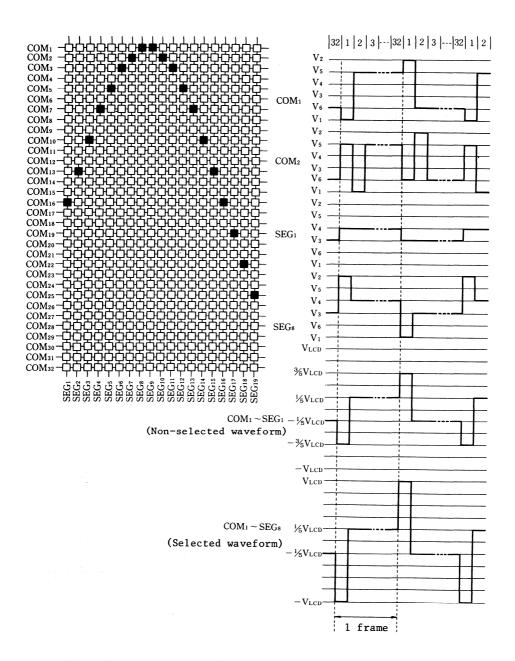

Example of Waveforms in 1/32 Duty Drive (Example of HD44102CH, HD44103CH)

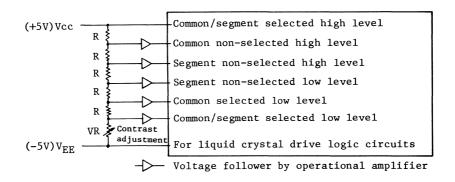

### POWER SUPPLY CIRCUIT FOR LIQUID CRYSTAL DRIVE

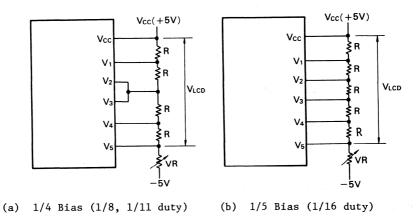

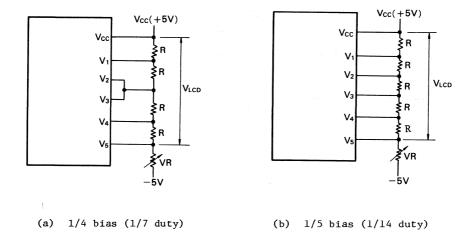

Table 1 shows the relationship between the number of driving biases and display duty ratios.

Table 1 Relationship between the Number of Dispaly Duties Ratio and the Number of Driving Biases

| Display<br>duty<br>ratio       | Static | 1/2               | 1/3  | 1/4   | 1/7 | 1/8  | 1/11      | 1/12 | 1/14 | 1/16 | 1/24        | 1/32 | 1/64 |

|--------------------------------|--------|-------------------|------|-------|-----|------|-----------|------|------|------|-------------|------|------|

| Number of<br>driving<br>biases | 2      | 3<br>(1/2<br>bias | (1/3 | bias) |     | (1/4 | 5<br>bias | )    |      | (1   | 6<br>I/5 bi | ias) |      |

#### • Drive in Resistance Dividing

A driving bias is generally generated in resistance dividing.

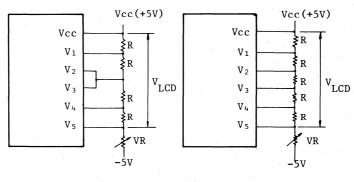

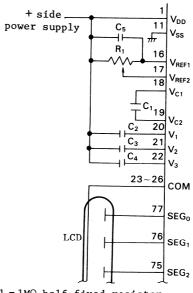

Fig. 12 Example of Driving Voltage Supply

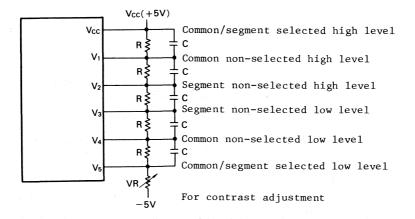

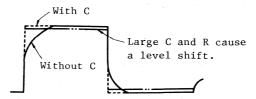

The setting of resistance value is determined by considering of operation margine and power consumption. Since the liquid crystal display load is capacitive, the drive waveform itself is distorted due to charge/discharge current when the liquid crystal display drive waveform is applied. To reduce distortion, the resistance value should be decreased but the power consumption increases because of the increase of the current through the dividing resistors. Since larger liquid crystal display panels have larger capacitance, the resistance value must be decreased.

Fig. 13 Example of Capacitor Connection for Improvement of Liquid Crystal Display Drive Waveform Distortion (1/5 bias) (Example of LCD-II)

It is efficient to connect a capacitor to the resistors in parallel as shown in Fig. 13 in order to improve charge/discharge distortion. However, the effect is limited. Even if it is attempted to reduce the power consumption with a large resistor and improve waveform distortion with a large capacitor, a level shift occurs and the operating margine is not improved.

Since the liquid crystal display load is of matrix configuration, the path of the charge/discharge current through the load is complicated. Moreover, it varies depending on display condition. Thus, a value of resistance cannot be simply determined from the load capacitance of liquid crystal display. It must be experimentally determined according to the demand for the power consumption of the equipment in which the liquid crystal display is incorporated.

Generally, R is  $1k\Omega$  to  $10k\Omega$ , and VR is  $5k\Omega$  to  $50k\Omega$ . No capacitor is used. A capacitor of  $0.1\mu F$  is usually used if necessary.

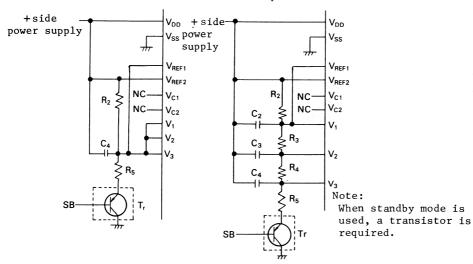

#### Drive by Operational Amplifier

In graphic display, the size of liquid crystal becomes larger and the display duty ratio becomes smaller, then the stability of liquid crystal drive level is more important than small display system.

Since the liquid crystal for graphic display is large and has many picture elements, the load capacity becomes large. The high impedance of the power supply for liquid crystal drive produces distortion in the drive waveforms, and deteriorates display quality. For this reason, the liquid crystal drive level should be low impedance with operational amplifiers. Fig. 14 shows an example of operational amplifier configuration.

Fig. 14 Drive by Operational Amplifier (1/5 bias)

No load current flows through the dividing resistors because of the high input impedance of operational amplifier. A high resistance of  $R=10k\Omega$  and  $VR=50k\Omega$  can be used.

#### Generation of Liquid Crystal Drive Level in LSI

The power supply circuit for liquid crystal drive level may be incorporated in the LSI such as for portable calculator with liquid crystal display.

HD61602, HD61603 for small display system has built-in power supply circuit for liquid crystal drive level.

# DATA SHEETS

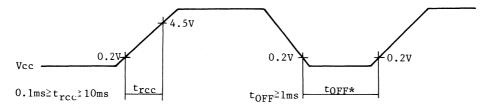

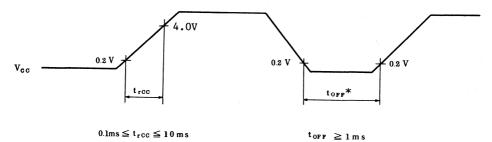

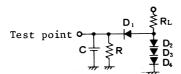

# • Precaution on Power Supply Circuit

The LCD driver LSI has two types of power supplies: the one for logical circuits and the other for liquid crystal display drive circuit. The power supply system is complicated because of several liquid crystal drive levels.

For this reason, in the power supply design, take care not to deviate from the voltage range assured in the maximum rating at the rise of power supply and from the potential sequence of each power supply. If the input terminal level is indefinite, through current flows and the power constantion increases because of the use of CMOS process in the LCD driver. Simultaneously, the potential sequence of each power supply becomes wrong, and a latch-up phenomenon may be caused.

# HD44100H (LCD DRIVER WITH 40-CHANNEL OUTPUTS)

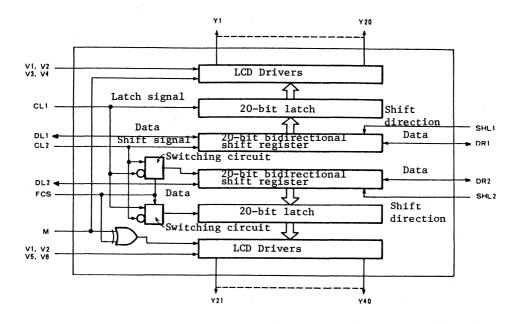

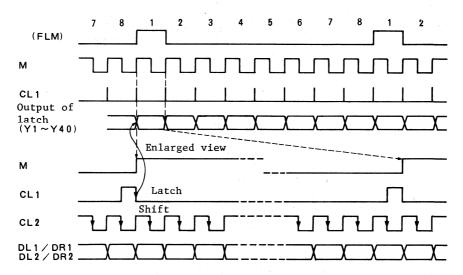

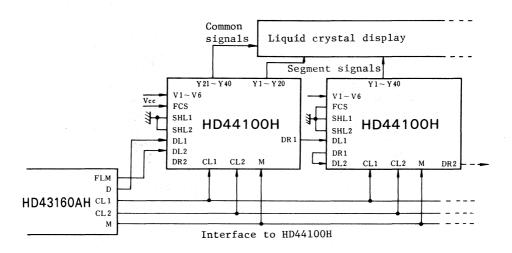

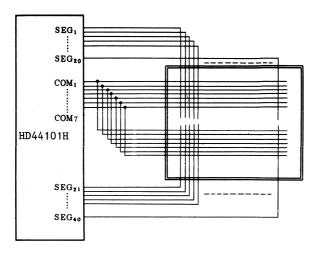

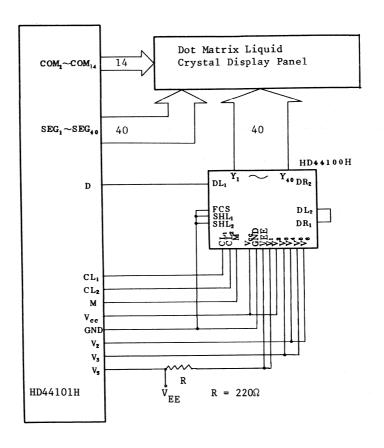

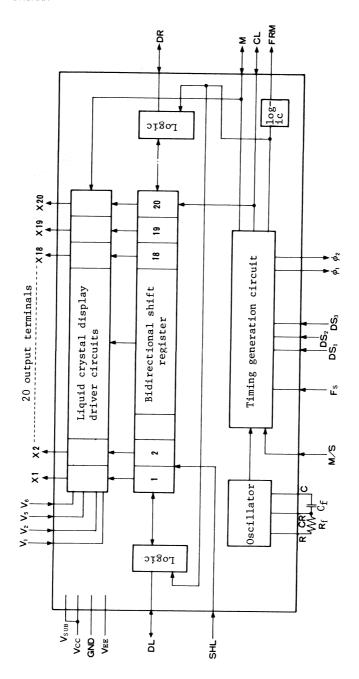

The HD44100H has two sets of 20-bit bidirectional shift registers, 20 data latch flip flops and 20 liquid crystal display driver circuits. It receives serial display data from a display control LSI, converts it into parallel data and supplies liquid crystal display waveforms to the liquid crystal.

The HD44100H is a liquid crystal display driver with high generalizability, which can drive a static drive liquid crystal and a dynamic drive liquid crystal, and can be applied to a common driver or segment driver.

- Liquid crystal display driver with serial/ parallel conversion function

- Serial transfer facilitates board design

- Capable of interfacing to liquid crystal display controllers: HD43160AH, LCTC (HD61830), HD44101H, LCD II (HD44780), LCD III (HD44790).

- Internal liquid crystal display driver ... 40 drivers

- Internal serial/parallel conversion circuits

20-bit shift register  $\times$  2 20-bit data latch  $\times$  2

• Display bias: Static ∿ 1/5

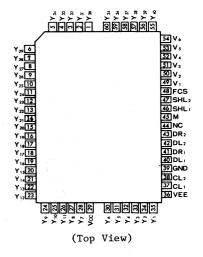

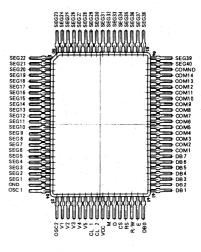

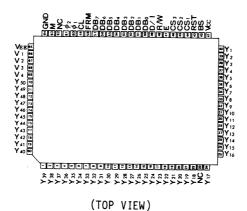

PIN ARRANGEMENT

#### • Power supply

Internal logic: +5V

Liquid crystal display driver circuit: -5V

The separation of internal logic from liquid crystal display driver circuit allows applicable controllers and liquid crystal types to increase.

- CMOS process

- 60-pin flat plastic package

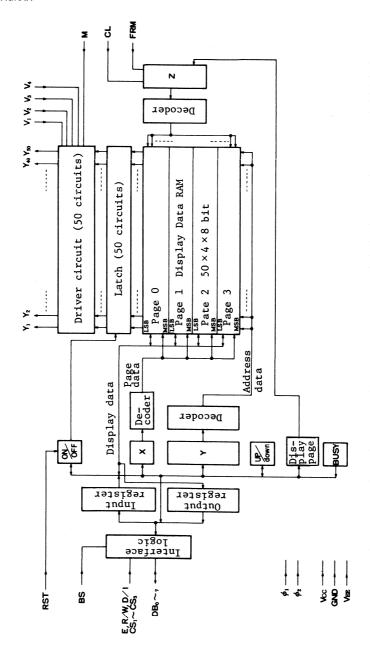

#### ■BLOCK DIAGRAM

#### ■ ABSOLUTE MAXIMUM RATINGS

|          | Item          | Symbol             | Value                              | Unit |

|----------|---------------|--------------------|------------------------------------|------|

| Supply   | Logic         | $v_{CC}$           | -0.3 to $+7.0$                     | V *1 |

| voltage  | LCD drivers   | V <sub>EE</sub> *2 | $V_{CC} - 13.5$ to $V_{CC} + 0.3$  | V    |

| Input vo | 1tage         | $v_{T1}$           | $-0.3$ to $V_{CC} + 0.3$           | V *1 |

| Input vo | 1tage         | V <sub>T2</sub> *3 | $v_{CC}^{+0.3}$ to $v_{EE}^{-0.3}$ | V    |

| Operatin | g temperature | Topr               | - 20 to +75                        | °C   |

| Storage  | temperature   | T <sub>stg</sub>   | -55 to +125                        | °C   |

- \*1 All voltage values are referenced to GND.

- \*2 Connect a protection resistor of  $220\Omega \pm 5\%$  to VEE power supply in series.

- \*3 Applies to  $V_1$  to  $V_6$

# ■ ELECTRICAL CHARACTERISTICS $(V_{CC} = 5V \pm 10\%, V_{EE} = -5V \pm 10\%, GND = 0V, Ta = -20 to + 75°C)$

| Item                     | Symbo1          | Applicable terminal                            | Test condition                           | min                   | typ | max                 | Unit |

|--------------------------|-----------------|------------------------------------------------|------------------------------------------|-----------------------|-----|---------------------|------|

| Input voltage            | νIΗ             | CL1,CL2,DL1,DL2,DR1,DR2,                       |                                          | 0.7 V <sub>CC</sub>   | -   | v <sub>CC</sub>     | V    |

| Input Voltage            | VIL             | M,SHL1,SHL2,FCS                                | ,                                        | 0                     | -   | 0.3 V <sub>CC</sub> | V    |

| Output voltage           | VOH             | DL1,DL2,DR1,DR2                                | I <sub>OH</sub> = -0.4mA                 | V <sub>CC</sub> - 0.4 | -   | -                   | v    |

| Output vortage           | VOL             | DGI,DGZ,DKI,DKZ                                | I <sub>OL</sub> = +0.4mA                 | -                     | -   | 0.4                 | v    |

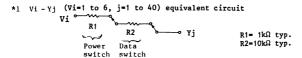

| Vi-Yj voltage            | V <sub>D1</sub> |                                                | ION = 0.1mA for one of Y1                | -                     | -   | 1.1                 | V    |

| descending               | v <sub>D2</sub> | *1                                             | I <sub>ON</sub> = 0.05mA for each Yi     | -                     | -   | 1.5                 | V    |

| Input leakage<br>current | IIL             | CL1,CL2,DL1,DL2,DR1,DR2,<br>M,SHL1,SHL2,FCS,NC | Vin = 0 to V <sub>CC</sub>               | -5.0                  | -   | 5.0                 | μΑ   |

| Vi leakage<br>current    | IVL             | *3                                             | Vin = V <sub>CC</sub> to V <sub>EE</sub> | -10.0                 | -   | 10.0                | μΛ   |

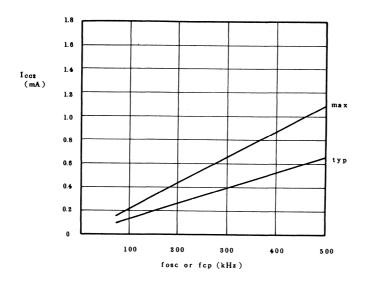

| Power supply             | ICC             | *2                                             | fCL2 = 400kHz                            | -                     | -   | 1.0                 | mA   |

| current                  | IEE             | 72                                             | f <sub>CL1</sub> = 1kHz                  | -                     | -   | 10                  | μA   |

- \*2 Input/output current is excluded; when input is at the intermediate level with CMOS, excessive current flows through the input circuit to the power supply. To avoid this, input level must be fixed at high or low.

- \*3 Output Y1 to Y40 open.

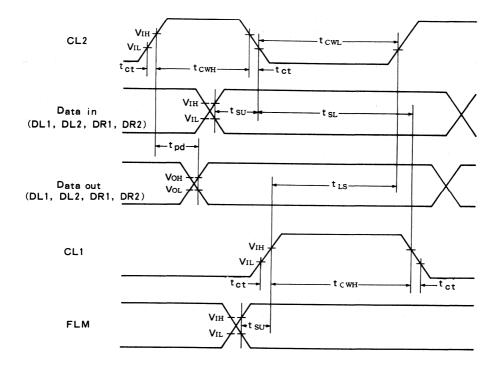

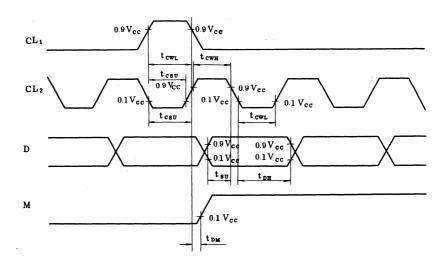

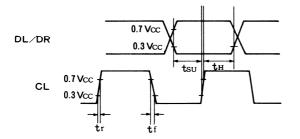

# ■ TIMING CHARACTERISTICS $(V_{CC} = 5V \pm 10\%, V_{EE} = -5 \pm 10\%, GND = 0V, Ta = -20 to + 75°C)$

|         | Item           | Symbol | Applicable terminal | Test<br>condition      | min | typ | max | Unit |

|---------|----------------|--------|---------------------|------------------------|-----|-----|-----|------|

| Data s  | hift frequency | fCL    | CL2                 |                        | -   | -   | 400 | kHz  |

| Clock   | High level     | t CWH  | CL1,CL2             |                        | 800 | -   | -   | ns   |

| width   | Low level      | tCWL   | CL2                 |                        | 800 | -   |     | ns   |

| Data s  | et-up time     | tSU    | DL1,DL2,DR1,DR2,FLM |                        | 300 | -   | -   | ns   |

| Clock : | set-up time    | tSL    | CL1,CL2             | (CL2→CL1)              | 500 | -   | _   | ns   |

| Clock : | set-up time    | tLS    | CL1,CL2             | (CL1→CL2)              | 500 | -   | -   | ns   |

| Data de | elay time      | tpd    | DL1,DL2,DR1,DR2     | C <sub>L</sub> = 15 pF | -   | -   | 500 | ns   |

| Clock : | rise/fall time | tct    | CL1,CL2             | .1 4                   | -   | -   | 200 | ns   |

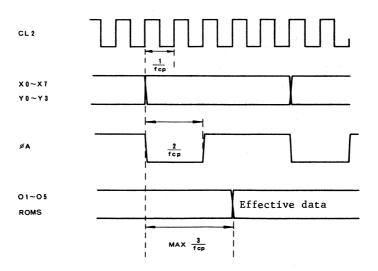

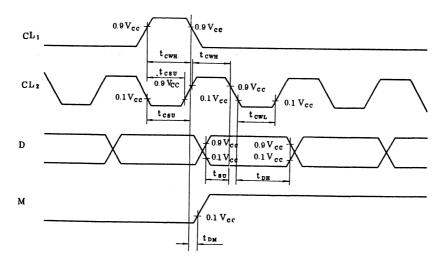

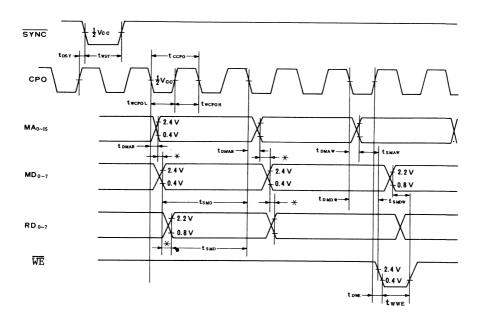

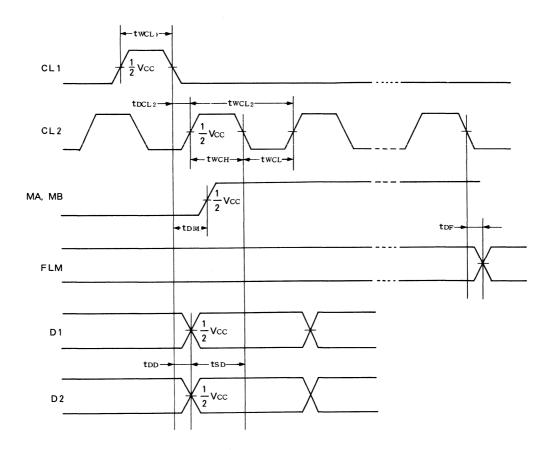

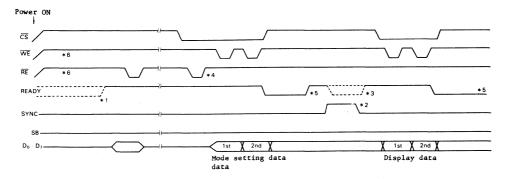

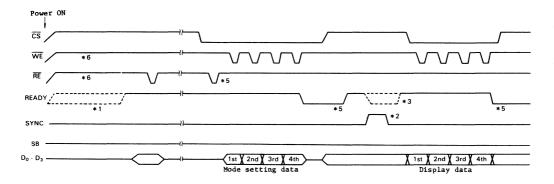

Fig. 1 Timing Waveform

Table 1 Fucntional Description of Terminals

| Signal<br>name | Number<br>of<br>lines | Input/<br>Output | Connected to              | Function                                                                                                                              |

|----------------|-----------------------|------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Vcc            | 1                     |                  | Power supply              | Power supply for logical circuit                                                                                                      |

| GND            | 1                     |                  | Power supply              | OV                                                                                                                                    |

| VEE            | 1                     |                  | Power supply              | Power supply for liquid crystal display drive                                                                                         |

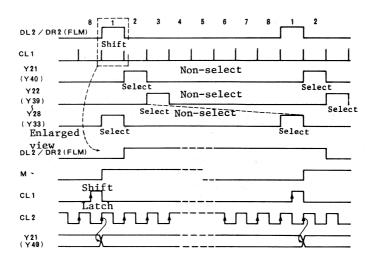

| Y1 ~ Y20       | 20                    | Output           | Liquid crystal            | Liquid crystal driver output (Channel 1)                                                                                              |

| Y21 ~ Y40      | 20                    | Output           | Liquid crystal            | Liquid crystal driver output (Channel 2)                                                                                              |

| $V_1, V_2$     | 2                     | Input            | Power supply              | Power supply for liquid crystal display drive (Select level)                                                                          |

| V 3, V 4       | 2                     | Input            | Power supply              | Power supply for liquid crystal dispaly drive (Non-select level for channel 1)                                                        |

| V5, V6         | 2                     | Input            | Power supply              | Power supply for liquid crystal display drive<br>(Non-select level for channel 2)                                                     |

| SHL1           | 1                     | Input            | VCC or GND                | Selection of channel 1 shift register in the shift direction                                                                          |

|                |                       |                  |                           | SHL1 DL1 DR1                                                                                                                          |

| :              |                       |                  | the state of the          | VCC OUT IN                                                                                                                            |

|                |                       |                  |                           | GND IN OUT                                                                                                                            |

| SHL2           | .1                    | Input            | V <sub>CC</sub> or GND    | Selection of channel 2 shift register in the shift direction                                                                          |

|                |                       |                  |                           | SHL2 DL2 DR2                                                                                                                          |

|                |                       |                  |                           | V <sub>CC</sub> OUT IN                                                                                                                |

|                |                       |                  | * -                       | GND IN OUT                                                                                                                            |

| DL1, DR1       | 2                     | Input/<br>output | Controller<br>or HD44100H | Data input/output of channel l shift register                                                                                         |

| DL2, DR2       | 2                     | Input/<br>output | Controller<br>or HD44100H | Data input/output of channel 2 shift register                                                                                         |

| М              | 1                     | Input            | Controller                | Alternated signal for liquid crystal driver output                                                                                    |

| CL1            | 1                     | Input            | Controller                | Shift signal for channel 1 (\(\bar{\pi}\)) *1 This is used for channel 2 when FCS is GND.                                             |

| CL2            | 1                     | Input            | Controller                | Latch signal for channel 1 ( L) *1 This is used for channel 2 when FCS is GND.                                                        |

| FCS            | 1                     | Input            | V <sub>CC</sub> or GND    | Mode select signal of channel 2. FCS signal exchanges the latch signal and the shift signal of channel 2 and inverts M for channel 2. |

|                |                       |                  | FCS level                 | Channel 2 M polarity Purpose                                                                                                          |

|                |                       |                  | FC3 Tevel                 | Latch signal Shift signal                                                                                                             |

|                |                       |                  | vcc                       | CL2 _ CL1 _ M For common drive                                                                                                        |

|                |                       |                  | GND                       | CL1 _ CL2 _ M For segment drive                                                                                                       |

|                | 1                     |                  |                           | *1 *1 *2                                                                                                                              |

<sup>\*1</sup>  $\mathcal{F}$  and  $\mathcal{L}$  indicate the latches at rise and fall times respectively.

$<sup>\</sup>star 2$  The output level relationship between channel 1 and channel 2 based on the FCS signal level is as follows:

| FOC             | D-4-         | v   | Output                | level                    |  |  |

|-----------------|--------------|-----|-----------------------|--------------------------|--|--|

| FCS             | Data         | М   | $1 (Y_1 \sim Y_{20})$ | $2 (Y_{21} \sim Y_{40})$ |  |  |

|                 | "1"          | "1" | $V_1$                 | V <sub>2</sub>           |  |  |

| v <sub>cc</sub> | (Select)     | "0" | V <sub>2</sub>        | Vı                       |  |  |

| ("1")           | "0"          | "1" | V <sub>3</sub>        | V <sub>6</sub>           |  |  |

|                 | (Non-select) | 0,, | V4                    | . V5                     |  |  |

|                 | "1"          | "1" | $v_1$                 | . V <sub>1</sub>         |  |  |

| GND             | (Select)     | "0" | V <sub>2</sub>        | V <sub>2</sub>           |  |  |

| ("0")           | "0"          | "1" | V <sub>3</sub>        | V <sub>5</sub>           |  |  |

| I               | (Non-select) | "0" | V.,                   | V <sub>6</sub>           |  |  |

<sup>&</sup>quot;1" and "0" indicate a high and low levels, respectively.

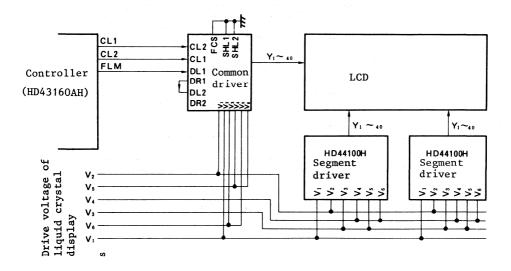

#### ■ APPLICATIONS

#### • Segment Driver

When the HD44100H is used as a segment driver, the FCS is set to GND to transfer display data in the timing shown in Fig. 2. In this case, both of channel 1 and channel 2 are shift data at the fall of CL2 and latch it at the fall of CL1.  $\rm V_3$  and  $\rm V_5$ ,  $\rm V_4$  and  $\rm V_6$  of power supply for liquid crystal display driver are short-circuited.

Fig. 2 Segment Data Waveforms (A type waveforms 1/8 duty)

#### • Common Driver

When channel 1 is used as a segment driver and channel 2 as a common driver. When channel 2 of HD44100H is used as a common driver, the FCS is set to  $V_{\text{CC}}$  level to transfer display data in the timing shown in Fig. 3. In this case, channel 2 shifts data at the rise of CL1 and latches it at the rise of CL2. Channel 1 has the same data as Fig. 2.

Fig. 3 Common Data Waveforms (A type waveforms of channel 2, 1/8 duty)

# When both Channel 1 and Channel 2 used as Common Drivers (FCS = GND)

When both of channel 1 and channel 2 of HD44100H are used a common driver, the FCS is set to GND and the signals (CL1, CL2, FLM) from the controller are connected to shown in following figure.

In this case, connection of power supply for liquid crystal display driver is different from segment driver, so refer to following figure.

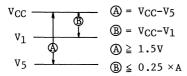

$V_1$ ,  $V_2$  ..... Select level of segment and common

V<sub>3</sub>, V<sub>4</sub> ..... Non-select level of segment

V<sub>5</sub>, V<sub>6</sub> ..... Non-select level of common

#### • Static Drive

When the HD44100H is used in the static drive, data is transferred at the fall of CL2 and latched at the fall of CL1. The frequency of CL1 becomes the frame frequency of liquid crystal display driver. The signal that has the frequency twice that of CL1 synchronized at the fall of CL1 is input into terminal M. The power supply for liquid crystal display driver is used by short-circuiting  $V_1$ ,  $V_4$  and  $V_6$ , and  $V_2$ ,  $V_3$  and  $V_5$ .

One of liquid crystal display driver output terminals can be used for a common output. In this case, the FCS is set to GND and data is transferred so that "O" can be always latched in the latch corresponding to the liquid crystal display driver output terminal used as the common output. If the latch signal corresponding to the segment output is "1", the segments of LCD light. They also light with common side = "1", and segment side "0".

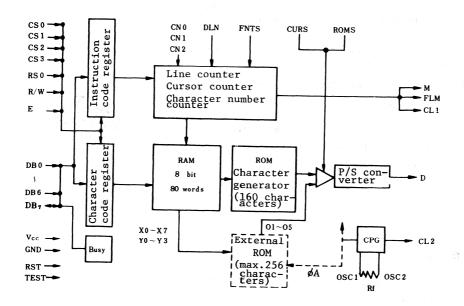

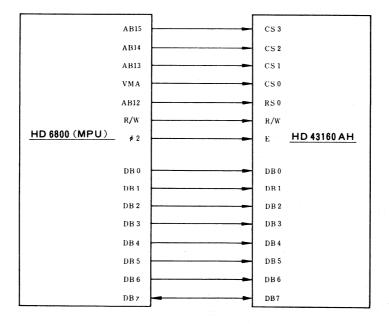

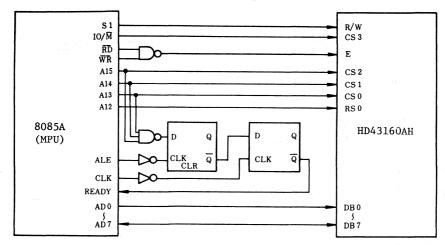

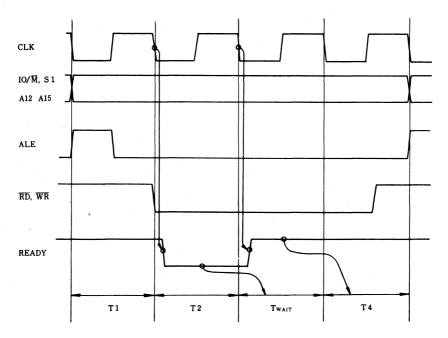

# HD43160AH (CONTROLLER WITH BUILT-IN CHARACTER GENERATOR)

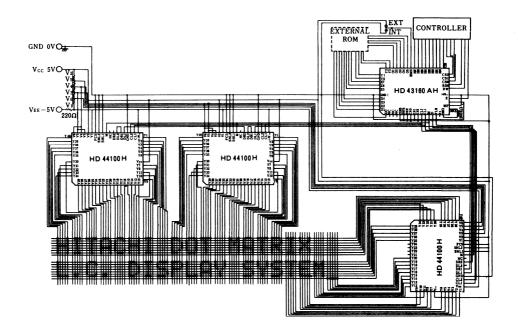

DISPLAY CONTROLLER AND CHARACTER GENERATOR

FOR DOT MATRIX LIQUID CRYSTAL DISPLAY SYSTEM

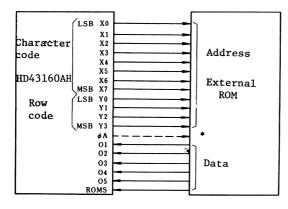

The HD43160AH receives character data written in the ASCII code or JIS code from micro-computer and stores them in its RAM which has 80 words capacity.

The HD43160AH converts these data into serial character pattern, then transfers them to LCD drivers.

It also generates other signals for LCD.

#### ■ CHARACTER DISPLAY

- Alphanumeric character; A ~ Z, a ~ z, @, #, %, &, etc.

- Japanese Character (katakana)

- 160 characters by internal character generator (ROM). (Max 256 characters by external ROM)

#### ■ NUMBER OF CHARACTERS

• 4, 8, 16, 24, 32, 40, 64 or 80 characters in 1 or 2 lines

#### ■ FRONT

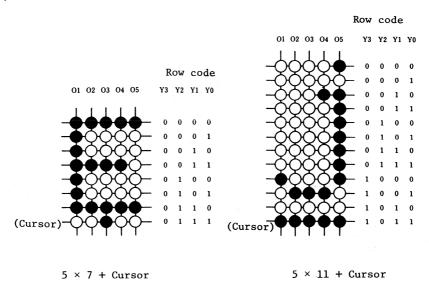

$\bullet$  5  $\times$  7 + Cursor or 5  $\times$  11 + Cursor

#### ■ OTHER FUNCTION CONTROLLED BY MICROCOMPUTER

- Display clear

- Cursor ON/OFF

- Cursor position preset (Character position)

- Cursor return

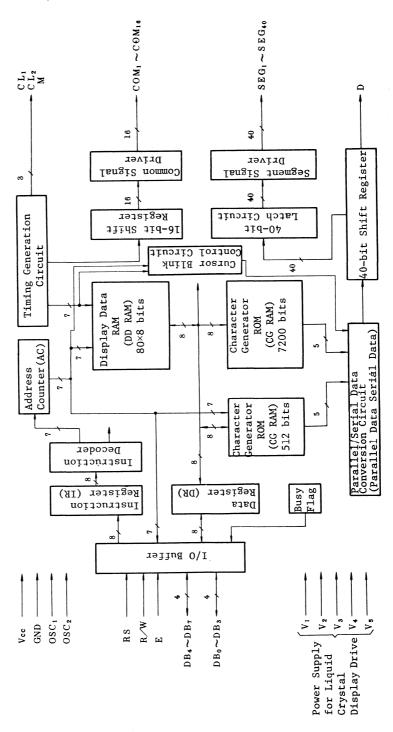

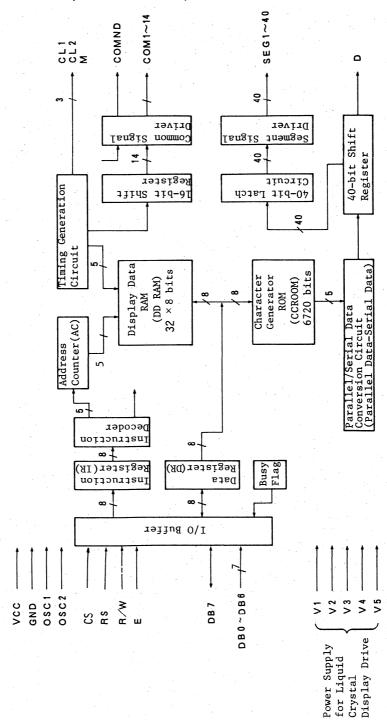

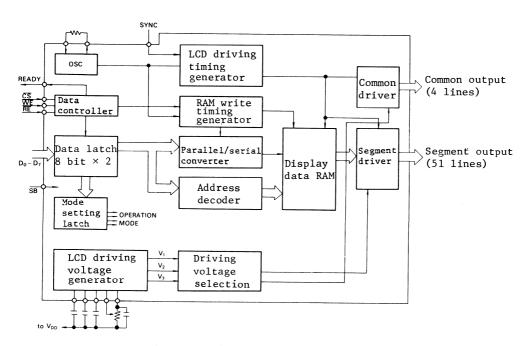

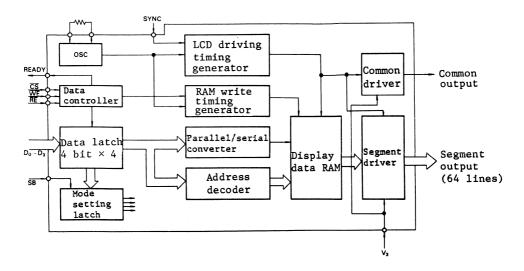

#### ■ BLOCK DIAGRAM

#### ■ ABSOLUTE MAXIMUM RATINGS

| Item                  | Symbol            | Value                   | Unit |

|-----------------------|-------------------|-------------------------|------|

| Supply voltage        | , V <sub>CC</sub> | -0.3 to +7.0            | V    |

| Input voltage         | ·V <sub>T</sub>   | $-0.3$ to $V_{CC}$ +0.3 | v    |

| Operating temperature | Topr              | -20 to +75              | °C   |

| Storage temperature   | Tstg              | -40 to +125             | °C   |

# ■ ELECTRICAL CHARACTERISTICS (V<sub>CC</sub>=5V±5%, GND=0V, Ta=-20 to +75°C)

| Item                  | Symbol           | Terminal No.                                                   | Test condition                                      | min                 | typ | max                 | Unit |

|-----------------------|------------------|----------------------------------------------------------------|-----------------------------------------------------|---------------------|-----|---------------------|------|

| Input voltage         | v <sub>IH</sub>  | CSO ~ CS3, E, R/W,                                             |                                                     | 2.0                 | -   | VCC                 | v    |

| (TTL compatible)      | VIL              | DBO ~ DB7, RSO                                                 |                                                     | 0                   | -   | 0.8                 | V    |

| 7                     | AIHC             | OSC1, TEST, RST, FNTS,                                         |                                                     | 0.7 V <sub>CC</sub> | -   | Vcc                 | V    |

| Input voltage         | VILC             | CURS, DLN, ROMS,<br>CNO ~ CN2, O <sub>1</sub> ~ O <sub>5</sub> |                                                     | 0                   | -   | 0.3 V <sub>CC</sub> | V    |

| Output voltage        | VOH              | DB7                                                            | I <sub>OH</sub> =-0.205mA                           | 2.4                 |     | -                   | V    |

| output vortage        | VOL              | DB7                                                            | I <sub>OL</sub> =1.6mA                              | -                   | -   | 0.4                 | V    |

| Output voltage        | VOHC             | FLM,M,D,CL1,CL2,                                               | Iload=±0.4mA                                        | VCC-1.0             | -   | -                   | v    |

| output vortage        | VOLC             | XO ~ X7, YO ~ Y3                                               | *10ad-20.4mA                                        | -                   | -   | 1.0                 | V    |

| Input leak current    | lin              | All inputs                                                     |                                                     | -5                  | -   | 5                   | μА   |

| Output leak current   | ILO              | DB7                                                            |                                                     | -10                 | -   | 10                  | μΑ   |

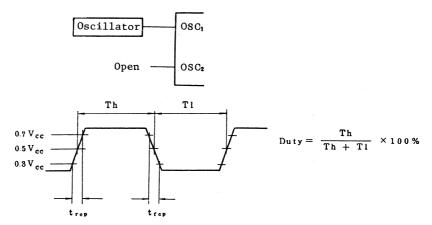

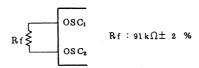

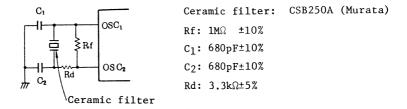

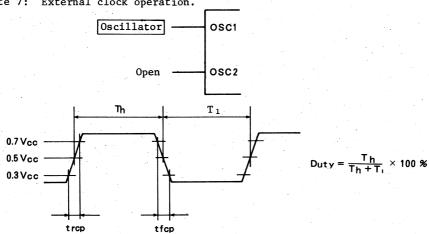

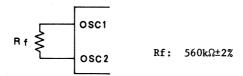

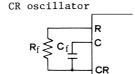

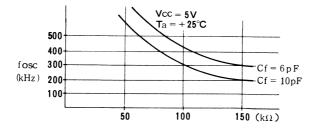

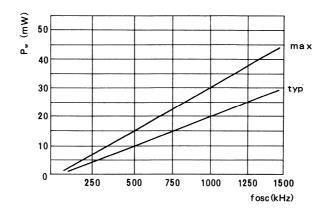

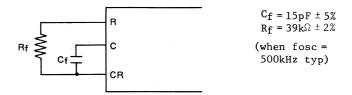

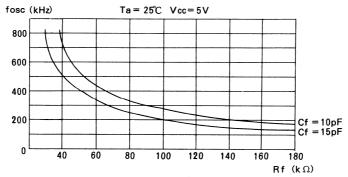

| Operating frequency   | f <sub>CP1</sub> |                                                                | R <sub>f</sub> =200kΩ±2%, 5×7+Cursor                | 130                 | 192 | 250                 | kHz  |

| operating frequency   | f <sub>CP2</sub> |                                                                | $R_{f}=130k\Omega\pm2\%$ , $5\times11+Cursor$       | 200                 | 288 | 375                 | kHz  |

| Input pull up current | I <sub>PL</sub>  | CSO ~ CS3, RSO, R/W,<br>DBO ~ DB7                              | V <sub>in</sub> =0V                                 | 2                   | 10  | 20                  | μA   |

| Power dissipation     | PT               | *                                                              | Ta=25c, f <sub>CP</sub> =400kHz<br>(external clock) |                     | -   | 10                  | mW   |

<sup>\*</sup> Input/output current is excluded. When input is at the intermediate level with CMOS, excessive current flows through the input circuit to the power supply. To avoid this, input level must be fixed at high or low, but CSO ~ CS3, RSO, R/W, DBO ~ DB7 are excluded.

# ■ PIN ARRANGEMENT

| Pin<br>No. | Power sup. | Input | Output | Pin<br>No. | Power sup.<br>OSC.  | Input | Output | Pin<br>No. | Power sup.<br>OSC. | Input | Output |

|------------|------------|-------|--------|------------|---------------------|-------|--------|------------|--------------------|-------|--------|

| 1          | GND (-)    |       |        | 19         | 1.0                 |       | D      | 37         |                    | DB3   |        |

| 2          |            |       | X4     | 20         |                     |       | FiM    | 38         |                    | DB4   |        |

| 3          |            |       | Х3     | 21         |                     |       | φА     | 39         |                    | DB5   |        |

| 4          |            |       | X2     | 22         | osc1                |       |        | 40         |                    | DB6   |        |

| 5          |            |       | X1     | 23         | OSC2                |       |        | 41         |                    | DB7   | DB7    |

| 6          |            |       | XO     | 24         |                     | RST   |        | 42         |                    | ROMS  |        |

| 7          |            |       | N.C.   | 25         |                     | TEST  |        | 43         |                    | 05    |        |

| 8          |            |       | N.C.   | 26         |                     | Е     |        | 44         |                    | 04    |        |

| 9          |            |       | N.C.   | 27         | V <sub>CC</sub> (+) |       |        | 45         |                    | 03    |        |

| 10         | THE STATE  | CURS  | a 17   | 28         | A.                  | R/W   |        | 46         |                    | 02    |        |

| 11         |            | FNTS  |        | 29         | 1 1 1 1 1 1 1 1 1   | RS0   |        | 47         |                    | 01    |        |

| 12         |            | DLN   |        | 30         |                     | CS0   |        | 48         |                    |       | Y3     |

| 13         |            | CNO   |        | 31         | 1.65                | CS1   |        | 49         |                    |       | Y 2    |

| 14         |            | CN1   |        | 32         |                     | CS2   |        | 50         |                    |       | Y1     |

| 15         |            | CN2   |        | 33         |                     | CS3   |        | 51         |                    |       | Y0     |

| 16         |            |       | C1.2   | 34         |                     | DB0   |        | 52         |                    |       | X7     |

| 17         |            |       | CL1    | 35         |                     | DB1   |        | 53         |                    |       | Х6     |

| 18         |            |       | М      | 36         |                     | DB2   |        | 54         |                    |       | X5     |

| ■ PI                     | N FUNCT               | ION                    |              |                                                                                                                                                                                                                                                                                                                        |

|--------------------------|-----------------------|------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin<br>name              | Number<br>of<br>lines | Connected to           | 1/0          | Function                                                                                                                                                                                                                                                                                                               |

| V <sub>CC</sub><br>GND   | 2                     | Power supply           |              | +5V ± 10% Power supply                                                                                                                                                                                                                                                                                                 |

| CNO<br>CN1<br>CN2        | 3                     | GND or V <sub>CC</sub> | I            | Total displayed character number select.   No. 4 8 16 24 32 40 64 80   CNO GND VCC GND VCC GND VCC GND VCC CN1 GND GND VCC VCC GND GND VCC VCC CN2 GND GND GND GND GND VCC VCC CN2 GND GND GND GND CCC VCC CN2 GND GND GND GND GND CCC VCC VCC VCC VCC VCC CN2 GND GND GND GND CN2 |

| CURS                     | 1                     | GND or V <sub>CC</sub> | I            | Cursor select VCC: 5 dots. •••• GND: 1 dot.                                                                                                                                                                                                                                                                            |

| DLN                      | 1                     | GND or V <sub>CC</sub> | I            | Display line number select. VCC: 2 lines. GND: 1 line.                                                                                                                                                                                                                                                                 |

| FNTS                     | 1                     | GND or V <sub>CC</sub> | I            | Font select.  VCC: 5 × 11 + Cursor.  GND: 5 × 7 + Cursor.                                                                                                                                                                                                                                                              |

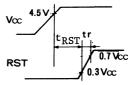

| RST                      | 1                     | v <sub>CC</sub>        | I            | Only for test. Normally $V_{\hbox{\scriptsize CC}}$                                                                                                                                                                                                                                                                    |

| TEST                     | 1                     | GND                    | I            | Only for test. Normally GND                                                                                                                                                                                                                                                                                            |

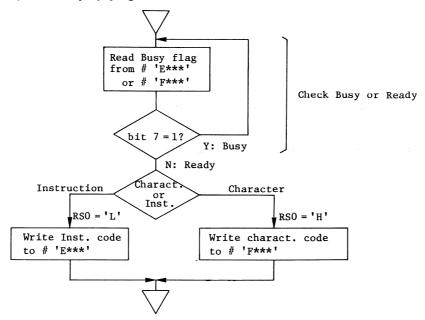

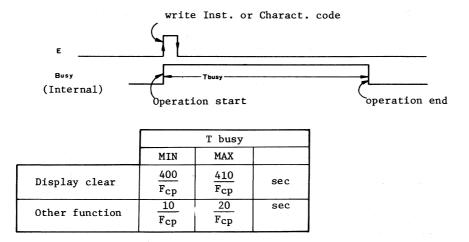

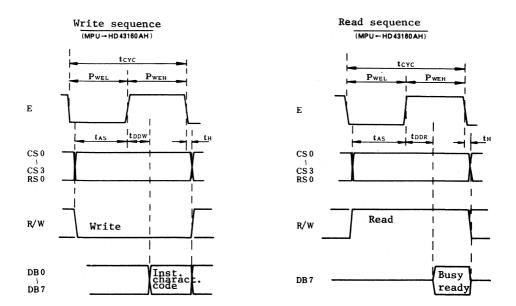

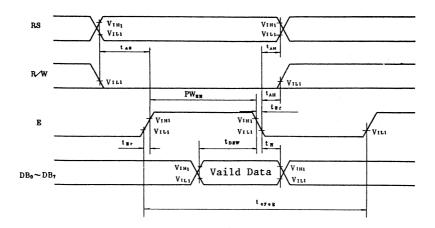

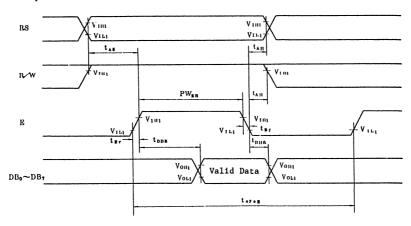

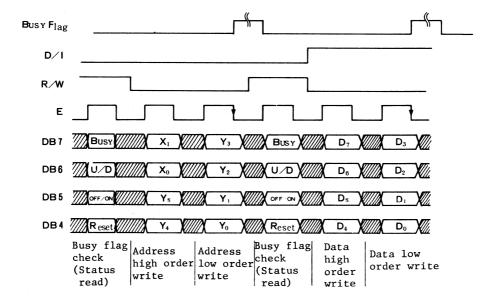

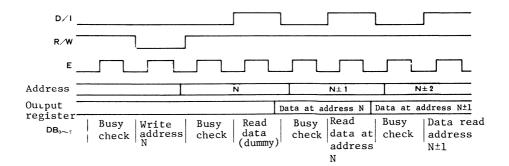

| Е                        | 1                     | MPU                    | I            | Strobe signal.  Write mode: The HD43160AH latches the data on DB0 ~ DB7 at the falling edge of this signal.  Read mode: Busy/Ready signal is active on DB7 while this signal is 'H'.                                                                                                                                   |

| R/W                      | 1                     | MPU                    | I            | Read/Write signal<br>L: HD43160AH gets the data from MPU.<br>H: MPU gets the Busy/Ready signal from<br>HD43160AH.                                                                                                                                                                                                      |

| CS0<br>CS1<br>CS2<br>CS3 | 4                     | MPU                    | I            | Chip select When all of CSO ${\sim}$ CS3 are 'H', HD43160AH is selected.                                                                                                                                                                                                                                               |

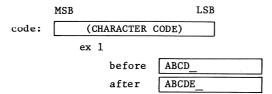

| RS0                      | 1                     | МРИ                    | I            | Register select.  HD43160AH has 2 registers. One is for Character code and another is for instruction code. Each register latches the data on DB0 ~ DB7 at the falling edge of 'E', when CS0 ~ CS3 are 'H' and R/W is 'L'. H; Character code register is selected. L; Instruction code register is selected.           |

| DB0                      | 8                     | MPU                    | I            | Data bus.                                                                                                                                                                                                                                                                                                              |

| ,<br>DR 7                |                       |                        | I/O<br>(DB7) | Inputs for Character code and Instruction code from MPU.                                                                                                                                                                                                                                                               |

| DB7                      |                       | IID//100m              | -            | Output for Busy/Ready flag (DB7).                                                                                                                                                                                                                                                                                      |

| D D                      | 1                     | HD44100H               | 0            | Serial dot data of characters for LCD drivers                                                                                                                                                                                                                                                                          |

| CL2                      | 1                     | HD44100H               | 0            | Dot data shift signal for LCD drivers.                                                                                                                                                                                                                                                                                 |

| CL1                      | 1                     | HD44100H               | 0            | Dot data latch signal for LCD drivers.                                                                                                                                                                                                                                                                                 |

| М            | 1                                      | нD44100н               | 0          | Alternate signal for LCD drivers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------|----------------------------------------|------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

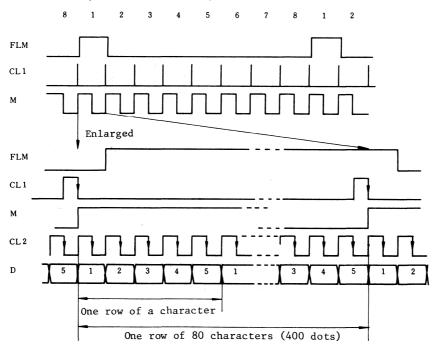

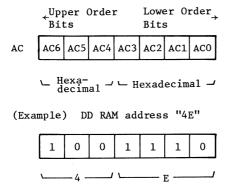

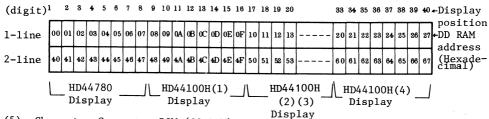

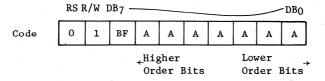

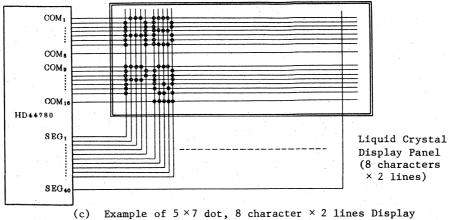

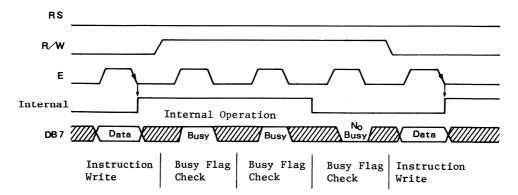

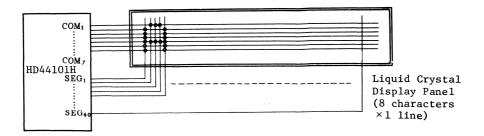

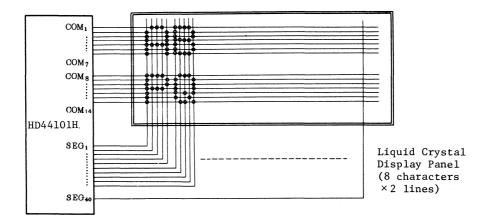

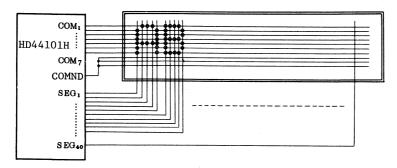

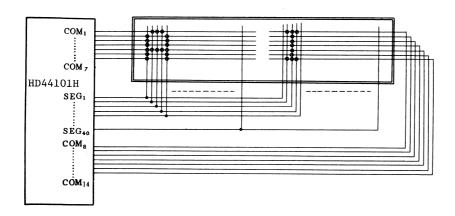

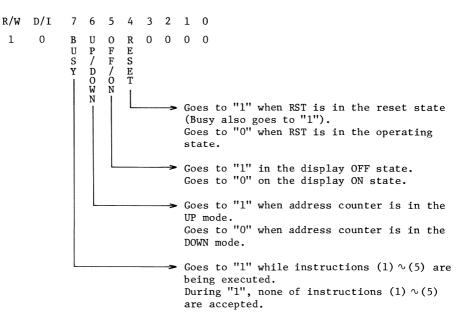

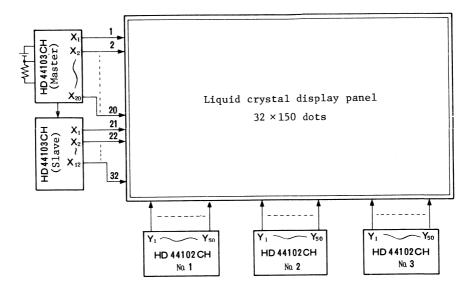

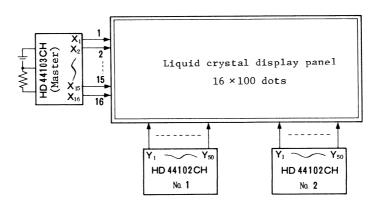

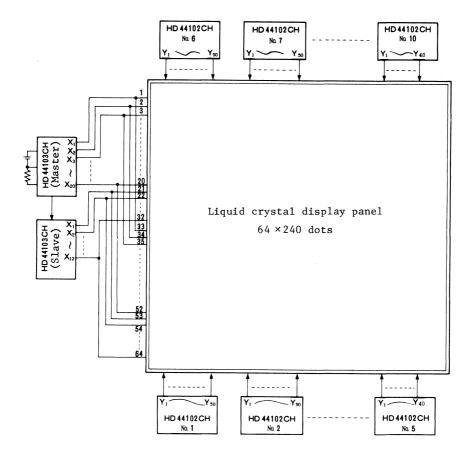

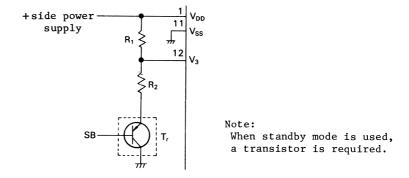

| FLM          | 1                                      | нD44100н               | 0          | Signal for common plates scanning.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |